Master's Thesis

# **Efficient Offloading of Network Functionalities** via ISA Extension

# **Description**

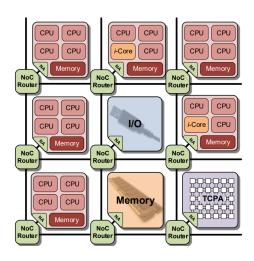

Hitting a wall is not a pleasant thing. Computer systems faced many walls in the last decades. Being able to break the memory wall in the mid 90's and the power wall in 2004, it now faces the next crucial barrier for scalabilty. Although being able to scale systems to 100's or 1000's of cores through NoCs, performance doesn't scale due to data-to-task dislocality. We now face the locality wall.

The newest trend to tackle this issue is data-task migration and processing in or near memory.

## Goal

The goal of this project is to efficiently offload network functionalities and near memory operations via ISA extension. A hardware prototype will be built.

## **Learning Objectives**

Towards this goal you'll complete the following tasks:

- Work in a bigger project and understand the concept of an existing HW platform

- Develop, implement and test an advanced hardware module on the given platform

- Compare/Evaluate the implementation with state of the art

- Document your work in a written thesis report and present your work in a presentation

# **Prerequisites**

To successfully complete this project, you should already have the following skills and experiences.

- Very good programming skills in VHDL

- Good programming skills in C

- Good comprehension of a complex system

- Very good knowledge about hardware development

#### Contact

Sven Rheindt, Room: N2140, Phone +49.89.289.28387, sven.rheindt@tum.de

## **Advisors**